Xilinx FPGA应用进阶 RAM IP核详解与设计开发实例

随着FPGA在数字信号处理、高速数据缓存和实时系统中的应用日益广泛,Xilinx提供的各类IP核成为提升开发效率、保证设计性能的关键工具。其中,RAM IP核作为最基础、最常用的存储解决方案,其灵活配置与高效使用对FPGA设计至关重要。本文将以Xilinx FPGA平台为例,深入详解RAM IP核的功能特性、配置方法,并通过一个完整的设计实例,展示从IP核生成到软件集成开发的完整流程。

一、RAM IP核核心功能与配置详解

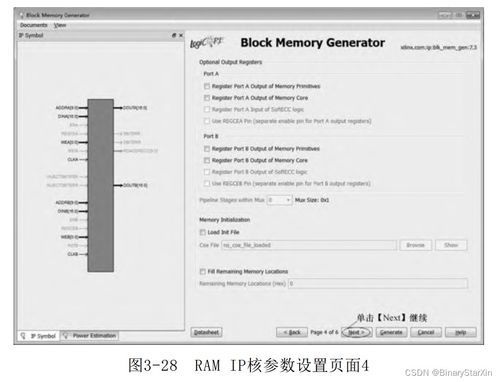

Xilinx Vivado设计套件中提供的Block Memory Generator IP核支持多种存储类型,包括单端口RAM、简单双端口RAM、真双端口RAM以及ROM。设计者可根据需求灵活选择。

- 关键配置参数:

- 内存类型:选择所需RAM类型,如单端口(读写共享一个端口)或双端口(可同时读写)。

- 端口宽度与深度:定义数据位宽和存储容量,需根据数据流和资源预算权衡。

- 操作模式:包括写优先、读优先和不变模式,影响读写冲突时的行为。

- 初始化文件:支持COE或HEX文件预加载初始数据,常用于ROM或RAM初始状态设置。

- 使能信号与复位:可选端口使能、写使能、复位信号,增强控制灵活性。

- 输出寄存器:添加输出流水线寄存器可提升时序性能,但增加一个时钟周期的读取延迟。

- 资源优化建议:

- 对于较大容量存储,Block RAM(BRAM)是首选,其功耗低、性能高。

- 小容量或分布式存储可选用LUT RAM,节省BRAM资源。

- 合理选择宽度与深度比例,使BRAM利用率接近100%,避免资源浪费。

二、RAM IP核生成与实例设计

以下是一个基于Vivado 2023.1的简单双端口RAM设计实例,实现一个数据缓存模块。

步骤1:创建IP核

在Vivado中新建工程后,通过“IP Catalog”搜索“Block Memory Generator”,双击打开配置界面。

步骤2:基本配置

- 选择“Simple Dual Port RAM”模式。

- 设置端口A为写端口,宽度16位,深度1024(即2KB容量)。

- 设置端口B为读端口,宽度16位,深度1024。

- 操作模式选择“No Change”,即读写冲突时保持输出不变。

- 勾选“Primitives Output Register”以提升时序。

- 可选加载初始化COE文件,本例留空。

步骤3:生成与封装

完成配置后,生成IP核。Vivado会自动产生封装文件(.xci)和实例化模板。在设计中可直接例化该模块。

步骤4:HDL代码实例化

以下为Verilog实例化示例:

`verilog

// 实例化生成的RAM IP核

blkmemgen0 yourraminstance (

.clka(clk), // 端口A时钟

.ena(wren), // 端口A使能

.wea(wren), // 端口A写使能(1为写)

.addra(wraddr), // 端口A地址

.dina(wrdata), // 端口A写入数据

.clkb(clk), // 端口B时钟(可与clka同源)

.enb(rden), // 端口B使能

.addrb(rdaddr), // 端口B地址

.doutb(rddata) // 端口B读出数据

);

`

三、软件开发与系统集成

在FPGA设计中,RAM常作为处理器(如MicroBlaze)的数据存储器或与自定义逻辑交互的缓冲区。集成开发通常涉及以下步骤:

- 总线接口集成:若RAM需被处理器访问,可通过AXI互联接口将其挂载到系统总线(如AXI4-Lite)。Vivado的IP集成器可图形化完成连接。

2. 驱动与软件访问:在Vitis统一软件平台中,可通过内存映射地址直接访问RAM。例如,在C代码中:

`c

#define RAMBASEADDR 0x40000000 // RAM的基地址(根据实际地址映射修改)

volatile uint16t *ramptr = (uint16t *)RAMBASEADDR;

// 写入数据

ramptr[offset] = datavalue;

// 读取数据

uint16t readvalue = ramptr[offset];

`

- 协同仿真验证:利用Vivado的仿真工具,编写测试平台验证RAM功能。可模拟读写序列,检查数据一致性和时序。

- 调试与优化:集成后,利用Vivado的ILA(集成逻辑分析仪)抓取实时信号,验证读写行为,并根据性能分析调整IP配置(如输出寄存器、时钟频率)。

四、进阶应用与注意事项

- 异步时钟域:双端口RAM支持异步时钟,但需谨慎处理跨时钟域问题,确保地址和数据信号同步。

- 错误检测与纠正:对于高可靠性应用,可启用ECC(错误校验与纠正)选项,但会额外占用资源。

- 功耗管理:在低功耗设计中,可动态控制RAM的使能信号,减少静态功耗。

- 与其它IP协同:在复杂系统中,RAM常与FIFO、DMA控制器等IP协同工作,构建高效数据通路。

Xilinx RAM IP核以其高度可配置性和可靠性,成为FPGA设计的基石。通过深入理解其参数含义,结合实际需求进行优化配置,并熟练运用Vivado与Vitis工具链进行集成开发,设计者能够构建出高性能、资源高效的存储子系统,为复杂FPGA应用奠定坚实基础。从单功能缓存到多处理器共享内存,RAM IP核的灵活运用贯穿FPGA设计的始终,是每一位FPGA工程师必须掌握的核心技能。